1. JFET Source-Follower Configuration

1.1 Tujuan

[KEMBALI] 1. Mengetahui karakteristik dan prinsip kerja dari rangkaian JFET Source-Follower

(Common Drain) Configuration

2. Membuat simulasi rangkaian di software

1.2 Pengertian

[KEMBALI] Setara JFET dari konfigurasi emitor-pengikut BJT adalah sumber-pengikut

konfigurasi, pada gambar dibawah perhatikan bahwa output dikeluarkan dari terminal sumber dan,

ketika catu daya DC diganti dengan hubungan arus pendek ekuivalennya, selokan dibumikan

(karenanya, terminologi umum-tiriskan).

1.4 Prinsip Kerja

Pertama, titik diam yang sesuai atau "titik-Q" perlu ditemukan untuk biasing yang benar dari rangkaian penguat (amplifier) JFET dengan konfigurasi penguat tunggal Common-source (CS), Common-drain (CD) atau Source-follower (SF) dan Common-gate (CG) yang tersedia untuk sebagian besar perangkat FET. Ketiga konfigurasi penguat amplifier JFET ini sesuai dengan konfigurasi common-emitter, emitter-follower, dan common-base menggunakan transistor bipolar.

Dalam tutorial tentang Penguat FET ini kita akan melihat Penguat JFET Common Source yang populer karena ini adalah desain penguat JFET yang paling banyak digunakan. Pertimbangkan konfigurasi rangkaian penguat Amplifier JFET Common Source

1.5 Dasar Teori

Setara JFET dari konfigurasi emitor-pengikut BJT adalah konfigurasi sumber-pengikut dari Gambar 9.24. Perhatikan bahwa output dikeluarkan dari terminal sumber dan, ketika suplai dc diganti dengan ekuivalen hubung singkatnya, maka drainase dibumikan (karenanya, terminologi common-drain).

[KEMBALI] Setara JFET dari konfigurasi emitor-pengikut BJT adalah sumber-pengikut

konfigurasi, pada gambar dibawah perhatikan bahwa output dikeluarkan dari terminal sumber dan,

ketika catu daya DC diganti dengan hubungan arus pendek ekuivalennya, selokan dibumikan

(karenanya, terminologi umum-tiriskan).

1.3 Komponen

[KEMBALI]

1.Resistor

Resistor sebagai penghambat arus pada rangkaian

2. Ground

Ground sebagai system pentanahan pada rangkaian

3. JFET

Sebagai penguat pada rangkaian

Pertama, titik diam yang sesuai atau "titik-Q" perlu ditemukan untuk biasing yang benar dari rangkaian penguat (amplifier) JFET dengan konfigurasi penguat tunggal Common-source (CS), Common-drain (CD) atau Source-follower (SF) dan Common-gate (CG) yang tersedia untuk sebagian besar perangkat FET. Ketiga konfigurasi penguat amplifier JFET ini sesuai dengan konfigurasi common-emitter, emitter-follower, dan common-base menggunakan transistor bipolar.

Dalam tutorial tentang Penguat FET ini kita akan melihat Penguat JFET Common Source yang populer karena ini adalah desain penguat JFET yang paling banyak digunakan. Pertimbangkan konfigurasi rangkaian penguat Amplifier JFET Common Source

1.5 Dasar Teori

Setara JFET dari konfigurasi emitor-pengikut BJT adalah konfigurasi sumber-pengikut dari Gambar 9.24. Perhatikan bahwa output dikeluarkan dari terminal sumber dan, ketika suplai dc diganti dengan ekuivalen hubung singkatnya, maka drainase dibumikan (karenanya, terminologi common-drain).

Mengganti rangkaian ekivalen JFET akan menghasilkan konfigurasi Gambar 9.25. Sumber yang dikontrol dan impedansi keluaran internal JFET terikat ke arde di satu ujung dan RS di ujung lainnya, dengan Vo melintasi RS. Karena gmVgs, rd, dan RS terhubung ke terminal dan ground yang sama, semuanya dapat ditempatkan secara paralel seperti ditunjukkan pada Gambar 9.26. Sumber arus berbalik arah tetapi Vgs masih didefinisikan antara terminal gerbang dan sumber.

Zi: Gambar 9.26 dengan jelas mengungkapkan bahwa Zi didefinisikan oleh

Zo: Pengaturan Vi 0 V akan menghasilkan terminal gerbang terhubung langsung ke ground seperti ditunjukkan pada Gambar. 9.27. Fakta bahwa Vgs dan Vo berada di seberang jaringan paralel yang sama menghasilkan Vo Vgs.

yang memiliki format yang sama dengan resistansi total dari tiga resistor paralel. Karena itu,

Untuk rd10RS,

dan menerapkan hukum tegangan Kirchhoff di sekeliling jaringan Gambar 9.26 akan menghasilkan

Dengan tidak adanya rd atau jika rd10RS

Karena bagian bawah Persamaan. (9.36) lebih besar dari pembilang dengan faktor satu, gain tidak akan pernah bisa sama dengan atau lebih besar dari satu (seperti yang dijumpai untuk jaringan BJT pengikut-emitor).

Hubungan Fase: Sejak Av Persamaan. (9.36) adalah jumlah positif, Vo dan Vi berada dalam fase untuk konfigurasi sumber-pengikut JFET.

Contoh Soal :

[KEMBALI]

Analisis dc dari jaringan sumber-pengikut Gambar. 9.28 akan menghasilkan VGSQ 2.86 V dan IDQ 4.56 mA.

(a) Menentukan gm.

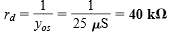

(b) Temukan rd.

(c) Tentukan Zi.

(D) Hitung Zo dengan dan tanpa rd. Bandingkan hasil.

(e) Tentukan Av dengan dan tanpa rd. Bandingkan hasil.

(a)

(b)

(c)

(d)

With rd:

mengungkapkan bahwa Zo sering relatif kecil dan ditentukan terutama oleh 1 / gram. Tanpa rd:

mengungkapkan bahwa rd biasanya berdampak kecil pada Zo.

(e)

With rd:

which is less than 1 as predicted above. Without rd:

mengungkapkan bahwa rd biasanya berdampak kecil pada perolehan konfigurasi

2. Rangkaian Simulasi

2.1 Gambar

[KEMBALI]

2.2 Vidio

[KEMBALI]

3. Download

[KEMBALI]

Tidak ada komentar:

Posting Komentar